炒股就看金麒麟分析师研报,权威,专业,及时,全面,助您挖掘潜力主题机会!

(来源:未来智库)

(报告出品方/作者:华创证券,岳阳)

一、先进封装是算力时代的关键,技术体系持续迭代升级

(一)算力需求激增,先进封装崛起为性能提升提供新引擎

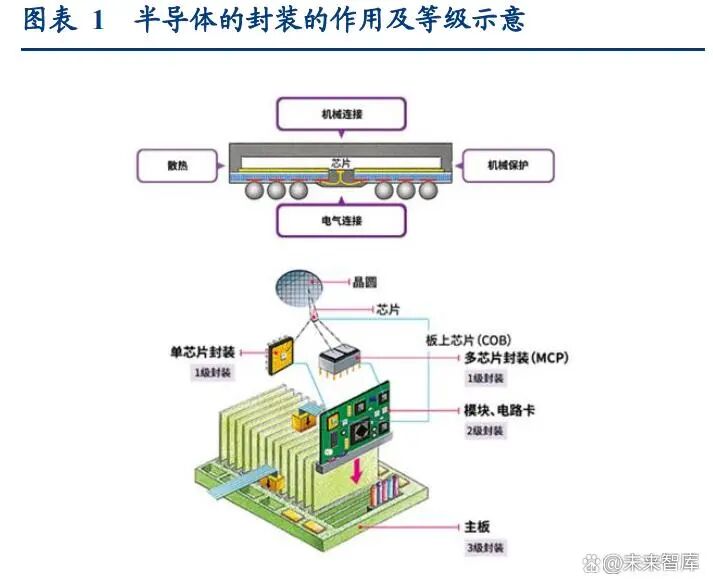

封装是半导体产业链的关键环节,负责实现芯片与外部电路之间的电气连接与机械保护。 半导体封装是集成电路制造的关键环节,负责实现芯片与外部电路之间的电气连接与机 械保护,并有效进行热管理,确保芯片在复杂工作环境下的可靠运行。传统封装技术, 如引线键合,通过将芯片固定在基板上并连接引脚,满足了早期集成电路的基本需求。 然而,随着摩尔定律的持续推进,芯片特征尺寸不断缩小,集成度呈几何级数增长,传 统封装在 I/O 密度、功耗、信号传输速度以及尺寸微缩方面的瓶颈日益凸显。 先进封装始终是动态演进的技术门槛,封装技术已历经五个主要发展阶段。先进封装本 质在于在互连密度、功耗、厚度或异构集成能力等核心指标上实现突破,推动行业技术 代际升级。根据《中国半导体封装业的发展》,全球集成电路封装技术已历经五个主要 发展阶段。当前,行业正向以台积电 CoWoS 为代表的 2.5D/3D 更高阶集成封装技术迈 进。

先进封装既是应对后摩尔时代挑战的关键,也是驱动新一轮行业格局变革的核心动力。 摩尔定律减速暴露“功耗墙、内存墙、成本墙”三重瓶颈,封装技术突破成为突破口。国 际半导体技术路线图(ITRS)指出,集成电路技术会沿 More Moore(延续摩尔定律)和 More than Moore(拓展摩尔定律)两个方向发展。过去几十年,摩尔定律推动集成电路 特征尺寸持续缩小,每两年晶体管密度翻番,带动芯片算力同步提升,但 2015 年以后, 集成电路制程的发展进入了瓶颈,7nm、5nm、3nm 制程的量产进度均落后于预期。随着 台积电宣布 2nm 制程工艺实现突破,集成电路制程工艺已接近物理尺寸的极限,集成电 路行业进入了“后摩尔时代”。 1)在 0.13um 节点后,漏电流激增、电压缩放受限,Dennard Scaling 效应失效,芯片 功耗难以有效抑制,散热压力成为性能进一步提升的主要障碍,“功耗墙”问题日益突 出。2)算力需求飙升,处理器性能与内存带宽差距不断扩大,AI 等高带宽场景下“内存墙” 成为系统效能短板。 3)先进制程开发成本激增,根据甬矽电子招股说明书援引 IC Insights,5nm 芯片研发 费用高达 5.4 亿美元,已是 28nm 的 10 倍,“成本墙”极大抬升了性能提升的边际代价。 上述多重制约,使单纯依靠制程微缩的摩尔路径渐趋极限,迫使产业链向封装等新型集 成技术寻求突破。

封装环节从“后工序”变成“性能发动机”,晶圆厂与 OSAT 共同推进技术突破。 制 程微缩红利减弱,先进封装已经不只是“装”,而是“参与芯片架构设计”的一部分,通过多 芯片集成、高密度互连、异构封装等方式,实现功能模块的灵活组合及性能提升,降低 能耗与成本。因此全球半导体产业链分工格局正在重塑,根据 Yole 的数据,2023 年先进 封装领域资本开支为 99 亿美元,主要来自台积电、英特尔、三星、SK 海力士等半导体 大厂,并预计 2024 年先进封装领域资本开支或增加到 115 亿美元。先进封装已占 IDM/ 晶圆厂 2023 年资本开支的 9%,约占头部 OSAT 的 41%。晶圆厂与 OSAT 均在加快向高 端封装布局,推动产业链价值重心前移。

AI 大模型及高算力应用推升算力需求,催生先进封装市场爆发式扩容。尤其是生成式 AI 带来的指数级算力需求,Deloitte《2025 global semiconductor industry outlook》 预计 2025 年生成式 AI 芯片销售额将突破 1500 亿美元,占半导体总收入逾 20 %。经中国信通院 《先进计算暨算力发展指数蓝皮书(2024 年)》测算,2023 年全球计算设备算力总规模 为 1397EFlops,增速达 54%,其中基础算力规模为 497 EFlops;智能算力规模为 875EFlops, 占总算力比例达到 63%,同比增加 13 个百分点;超算算力规模为 25EFlops。与此同时, 台积电在业绩会上披露, 25 年将持续大力扩产,目标 CoWoS 产能翻倍,但 2026 年前 供给或仍难追上 hyperscaler 与 GPU 厂商的排产需求,将先进封装从成本中心推向为价值 中心。

(二)封装结构演进路径:异构集成与 Chiplet 架构趋势成为产业发展焦点

近年来,先进封装的技术发展方向主要朝两个领域发展: 制程上探——晶圆制程领域:属于以单一功能芯片的高密度互联和电气性能优化为 核心的同构集成结构。在晶圆级封装(WLP)基础上不断发展,为了在更小的封装 面积下容纳更多引脚,利用晶圆上制作凸点工艺(Bumping)、晶圆重构工艺、硅通 孔技术(TSV)、晶圆扇出技术(Fan-out)、晶圆扇入技术(Fan-in)等技术。 系统下沉——集成模组领域:以系统级封装(SiP)为代表,包括采用了 FC、2.5D、 3D 等技术的系统级封装产品,将以前分散贴装在 PCB 板上的多种功能芯片集成为 一颗芯片,压缩模块体积、缩短电气连接距离以提升芯片系统功能,代表侧重异构 集成的发展方向。

主流先进封装结构在集成形式和工艺复杂度等方面各具技术优势,面向不同应用场景各 具优势: Flip-Chip(倒装封装):通过将芯片翻转,使 I/O 焊球直接与基板连接,取代传统 引线键合方式,大幅提升互联密度、散热效率和信号传输速度,具备更优的电气性 能。该结构支持多芯片集成和紧凑排布,兼具集成度和成本优势,是最早大规模商 用的先进封装形式之一,主要用于 CPU、智能手机和射频 SiP 解决方案。 晶圆级封装(WLP/Fan-Out):WLP 以整片晶圆为单位进行封装加工,与 FC 相比, WLP 的芯片与 PCB 之间没有基板,而是重布线层 RDL,封装尺寸接近芯片本体, 具备小型化、低成本等优势。目前 WLP 分为扇入型(WLCSP)和扇出型(FO), 两者差异为 RDL 布线是否可以向外,Fan-Out 通过重构晶圆边界区域并进行重新布 线,使 I/O 数目超出芯片本身限制,有效提升引脚密度与散热性能。广泛应用于对尺寸敏感、集成度要求高的领域,包括手机 AP/PMIC、射频前端、消费电子处理器等。

2.5D 封装(硅中介层集成):2.5D 将处理器、存储等若干个芯片并列排布在中介层 (Interposer)上,利用 RDL、硅桥、硅通孔(TSV)等技术实现更高密度的互联。 2.5D 具备更高的集成密度和更优异的热管理能力,适合高算力与高带宽需求场景。 例如台积电 CoWoS 系列即采用 2.5D 封装,为 FPGA、GPU 等高性能产品集成提供 解决方案。

3D 封装(硅通孔垂直堆叠):3D 封装利用硅通孔(TSV)等垂直互联技术,将多个 芯片堆叠贯穿,并直接与基板相连。该结构可有效降低封装面积与功耗,支持内存、 逻辑芯片的高密度集成,是提升带宽密度与容量的关键技术路径。该技术最早在 CMOS 图像传感器中应用,目前可用于 DDR、HBM 等存储芯片封装及部分 3D 逻辑 芯片等领域,技术难度最高。

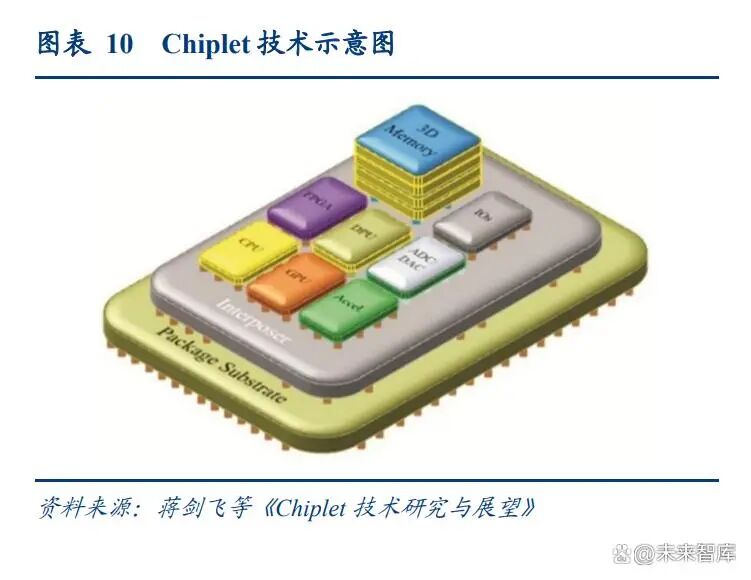

随着芯片复杂性与成本压力提升,Chiplet 架构逐渐成为异构集成和系统级平台化发展的 关键方向。Chiplet 是在多芯片模组(MCM)基础上发展出的新型封装架构,将单一复杂 芯片拆分为多个小型、独立且可复用的芯粒单元,并利用 Flip-Chip、2.5D 或 3D 等先进 封装技术实现不同工艺、材料和功能芯片的灵活组合。相比传统单芯片 SoC 方案,Chiplet 方案在良率、性能和成本方面优势明显:一是小芯粒提升晶圆良率,降低生产风险;二 是多芯片分布式架构满足高效能计算和扩展需求;三是异构芯片的灵活集成提升设计灵活性,有效控制成本。

Chiplet 方案+CoWoS 封装,已成为高端算力芯片主流配置。Chiplet 架构以其灵活的异构 集成能力和系统扩展性,逐渐成为高端算力芯片的主流方案。在实际落地过程中,以台 积电 CoWoS(Chip-on-Wafer-on-Substrate)为代表的 2.5D 封装平台,为多颗逻辑芯粒与 高带宽存储(HBM)之间的超高密度互联提供了成熟的工艺路径。据 Trendforce 信息, 当前,英伟达、AMD 等的先进 AI 芯片均基于 CoWoS 平台实现落地量产。

(三)核心工艺驱动技术突破,助力先进封装高密度集成加速

先进封装高密度集成的实现,依赖于一系列高精度工艺的持续突破。核心工艺不仅决定 了封装的 I/O 密度、系统性能和良率水平,也是产业链突围和价值提升的关键所在。

凸块工艺(Bumping):是实现芯片与基板、电路间高密度互联的基础。该工艺通 过在芯片表面形成微小金属焊球,为 Flip-Chip 等多种先进封装提供了物理与电气连 接点。工艺难点在于焊球阵列的一致性、共面度及尺寸精度,对设备和材料提出极 高要求。随着封装密度提升,凸块工艺的制程能力直接影响整体性能。

重布线层(RDL):提升引脚数量和信号灵活性的核心环节。RDL 通过在芯片表面 重新布线,将 I/O 信号从原有分布引至更大面积或指定位置,有效突破传统封装 I/O 瓶颈。高阶 RDL 需实现更细线宽与多层堆叠,考验光刻、蚀刻、镀膜等核心工艺能 力。当前高端 RDL 设备和核心材料仍由美日企业主导,国产厂商亟需攻关突破。

硅通孔(TSV):支撑 3D 封装及高带宽堆叠集成。TSV 通过在硅片内垂直刻蚀微 孔并金属填充,实现芯片间的高速垂直互联。关键工艺包括深硅刻蚀(DRIE)、铜 填充、孔隙控制与后续表面抛光。工艺难点在于高深宽比、孔径均匀性及填充致密 度,对设备和工艺参数协同要求极高。TSV 已成为 HBM、3D NAND 等产品高密度 集成的基础,但其量产良率和成本优化仍高度依赖设备材料的持续迭代。

混合键合(Hybrid Bonding):重塑芯片级互联密度极限。混合键合通过实现金属 -金属与介质-介质原子级直接结合,大幅缩短信号路径、降低互联电阻,实现超高密 度芯片集成。该工艺要求极致的表面平整度和纳米级对准精度,涵盖清洗、CMP、 超精密键合等全流程工艺设备协同。当前全球仅少数企业掌握混合键合量产工艺, 成为 Chiplet、3D 集成等新型高端封装的核心壁垒。

二、全球先进封装市场持续扩容,工艺升级不断驱动产业发展

(一)全球先进封装市场不断增长,2.5D/3D 等高集成技术促进结构升级

全球先进封装市场步入高景气通道,市场规模占据封测行业半壁江山。据 Yole 及中商产 业研究院数据测算,2024 年全球先进封装市场规模约为 450 亿美元,占全球半导体封装 市场总额的 55%左右。随着 AI、高性能计算、5G、汽车电子等下游需求拉动,Yole 预计 到 2030 年全球先进封装市场规模将增长至约 800 亿美元,2024-2030 年复合年增长率达 到 9.4%,成为推动半导体行业价值升级的核心环节。

先进封装向系统集成、高速、高频、三维方向发展,2.5D/3D 技术份额快速增长。根据 Yole,从技术结构看,2023 年,Flip-Chip 是先进封装最大细分领域,市占率约 44%。受 AI 与高端算力芯片需求驱动,2.5D/3D 封装技术份额快速提升。Yole 预计,2.5D/3D 封 装占比有望从 2023 年的 27%上升至 2029 年的 40%,营收年均复合增速高达 18.05%,远 超整体行业水平,成为市场结构升级的关键动力。整体来看,全球先进封装市场正由传 统 Flip-Chip 主导,逐步迈向以 2.5D/3D 和 Chiplet 为代表的高集成度、异构架构发展阶 段。

高带宽/高互连技术成为增量核心,高端性能封装 2030 年规模接近 285 亿美元。据 Yole 的高端性能封装拆分显示,2024 年后市场进入快车道,2024-2030 年间的复合年增长率 将达 23%。从结构看,Active Si Interposer、HBM 与 3D NAND Stack 等技术贡献度持续 抬升。其中, Active Si Interposer 受益于数据中心 AI 加速卡与 Chiplet 架构渗透,HBM 由 AI 训练和高性能计算对高带宽需求驱动,3D NAND Stack 则依托智能终端与服务器 对高密度存储的需求持续放量。

(二)下游需求多点开花,AI、汽车电子与智能终端成为主要增量来源

当前,先进封装市场的增长动力呈现出“AI、汽车电子孕育新机遇”的结构性特征。

1、HBM+CoWoS 成为 AI 算力芯片标配,驱动先进封装市场高速增长

AI 大模型与高性能计算的崛起,使服务器对带宽与存储提出极致需求。随着 ChatGPT 等 生成式 AI 加速落地,大模型训练参数规模迅速从数十亿级跃升至万亿级。据华尔街见闻 援引 SemiAnalysis 数据,GPT-4 训练所用 token 规模达到 13 万亿,单次训练成本高达 6300 万美元。如此大规模模型训练涉及 TB 级数据并行处理,服务器对算力、内存带宽、 延迟和功耗的要求大幅提升。此外,AI 推理环节同样面临高数据吞吐、低延迟的严苛考 验。传统的服务器架构采用 CPU/GPU 配合 DDR 内存的方案,在带宽密度、数据吞吐能 力上已无法支撑大规模 AI 场景的极致需求,迫切需要更高性能、更低延迟的存储解决方 案。

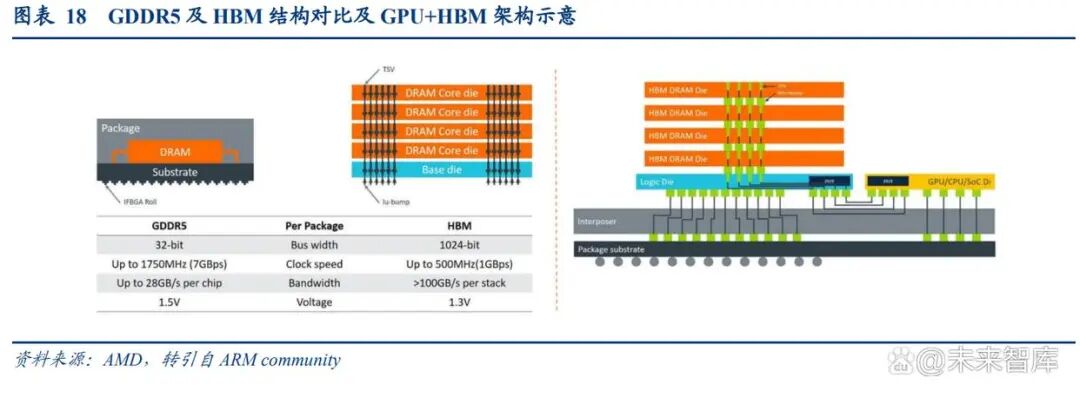

HBM 存储以高带宽、高密度和低功耗优势,成为 AI 服务器的标准配置。HBM 采用先 进 3D 堆叠封装技术,通过硅通孔(TSV)垂直堆叠多颗 DRAM 芯片,并在底部集成逻 辑芯片调度信号,在极小的面积上实现超高的数据吞吐,单颗带宽可超 1TB/s,较传统 GDDR6 提升 5 倍。物理布局上,HBM 堆叠体通常直接位于高性能逻辑芯片(如 GPU、 AI 加速器)侧边,通过宽总线接口与主芯片连接。 “近距离、宽总线”架构极大缩短信 号传输路径、降低延迟并提升能效,成为 AI 服务器大规模部署的核心基础。

AI 服务器市场高增长带动 HBM 渗透率迅速提升,2030 年渗透率有望达 50%。据 TrendForce 数据,2024 年全球 AI 服务器出货量预计达到 172.3 万台,同比增长 46%,占 整体服务器出货量的 12.6%;预计 2028 年将进一步提升至 20%左右,2023-2028 年出货 量复合增长率达 24%。在 AI 服务器市场,中高端 GPU(如英伟达 H200/B200/B300、AMD MI 系列)几乎全部标配 HBM,渗透率接近 100%。随着 AIGC 模型复杂度提升,推理端 对高带宽内存的需求同样加速释放,进一步推动 HBM 需求持续增长。据芯语转引 Yole 预测,全球 HBM 收入将从 2024 年的 170 亿美元增长至 2030 年的 980 亿美元,年复合 增速达 33%;在 DRAM 市场的收入份额占比也将从 18%升至 50%。

AI 算力需求爆发推动 2.5D/CoWoS 等高端工艺产能持续扩张,成为先进封装市场增量的 核心来源。HBM 的技术突破不仅源于自身工艺升级,更依赖于 2.5D 先进封装中硅中介 层的精密布线能力。以台积电 CoWoS 平台为例,可在 1 平方厘米内布设超过 10 万微凸 点,实现 GPU/AI 处理器与 HBM 间的超高密度互联,将芯片间物理距离缩短至微米级, 显著提升系统带宽与能效。AI 服务器高景气将直接带动 CoWoS 产能扩张和设备投资, 成为驱动先进封装市场高增长的重要动能。

2、汽车电动化+智能化双轮驱动,打开先进封装蓝海市场

全球新能源汽车渗透率持续提升,我国新能源汽车产业发展领跑全球。近年我国新能源 汽车发展迈入快车道,2024 年中国新能源汽车销量近 1287 万台,渗透率达到 40.9%;据 上海证券报援引中国电动汽车百人会预测,乐观估计 2025 年我国新能源车内需有望达到1500 万辆,渗透率将会超过 55%。根据乘联会分会数据,2024 年全球新能源车销量达到 1603 万辆,渗透率仅为 18%,未来有望渗透率有望不断提升,带动配套产业链稳步增长。

汽车智能化升级不断推进,带动单车芯片用量显著提升。据半导体产业纵横测算,传统 燃油车所需芯片数量约为 600 至 700 颗,电动车因三电系统和电子控制单元增加,芯片 用量提升至 1600 颗左右;而智能汽车在感知、决策、执行等系统中的计算与传感需求更 为密集,单车芯片数量突破 3000 颗,较电动车时代再次实现接近翻倍增长,芯片单车价 值量随之提升,汽车电子已成为半导体市场需求增长的重要下游之一。

自动驾驶等级提升,显著推高车规芯片对高算力与高可靠封装的双重要求。随着自动驾 驶向 L5 级进阶,芯片系统对算力需求呈指数级增长。高阶自动驾驶要求汽车承担更多决 策控制功能,对环境感知、高精度定位、路径规划、执行控制等关键环节提出极高的实 时性、准确性和容错性要求。例如域控制器芯片,需融合大量传感器数据、运行复杂 AI 推理及决策算法,确保在任何工况下无故障运行,封装环节也被赋予更高的质量标准。

高算力与高可靠性并重,先进封装正加速在车规芯片领域渗透应用。SiP(系统级封装)、 Chiplet 异构集成等先进封装技术,能够实现多功能芯片在单一封装体内的高效协同,大 幅提升系统性能和安全冗余,同时降低互连损耗、优化热管理。当前,英飞凌、恩智浦及 国内比亚迪半导体等主流车规芯片企业正加速导入先进封装方案,为自动驾驶和新能源 汽车产业升级提供坚实技术支撑,也将成为先进封装市场的重要增长引擎。

3、消费电子市场回暖与可穿戴设备放量,2D 主流封装需求稳步增长

消费电子市场企稳回暖,2D 先进封装存量板块稳定增长。2024 年以来,随着渠道库存压 力缓解,智能手机、平板、笔记本等主流产品销量逐步企稳回升。Canalys 数据显示,2024 年全球智能手机出货量增长 7%至 12.2 亿部,结束两年下滑趋势。PC 端由于商用 PC 部 署及日本市场需求拉动,2025 年二季度全球 PC 终端同比增长 7.4%至 6760 万台。另外, Windows 10 支持终止将在今年剩余时间内带来增长势头。WLP(尤其是 FOWLP)等轻 薄化、散热性能优良、性价比高的先进封装技术被消费终端产品广泛采用,全球消费电 子市场趋于稳健,为先进封装市场提供了坚实“基本盘”。

AI 终端市场加速成长,为相关先进封装市场打开新一轮增量空间。随着 AI 大模型商业 化应用加快,全球主要厂商持续加大对 AI 手机、AI PC 和可穿戴设备的布局。以 AI Agent 为代表的智能终端正拓展多元“AI+”应用场景。通富微电公告援引 IDC 预测,2024-2027 年全球 AI 手机出货量将由 0.4 亿台增至 1.5 亿台,渗透率跃升至 51.9%。同时,AI 眼镜、 AI 耳机等可穿戴新品类集成摄像头、传感器及 AI 算法,在翻译、导航、健康等多场景加 速渗透。Technavio 预计,2024-2029 年全球智能眼镜市场新增规模将达 9060 万美元,年 复合增速高达 14.5%。整体来看,AI 终端市场快速扩容,有望持续带动 WLP、Flip-Chip 等高密度先进封装用量,成为消费电子相关市场新的结构性增量引擎。

三、下游应用高成长叠加国产替代需求,国产先进封装大有可为

(一)中国先进封装市场渗透空间广阔,国产 OSAT 龙头加速布局

中国先进封装市场保持高增速,整体规模快速扩容,渗透率空间仍大。据锐观产业研究 院数据,2024 年,中国先进封装市场规模达 698 亿元,较 2020 年 351 亿元接近翻番,年 复合增长率达 18.7%,在全球先进封装市场中占比约 18.7%;2025 年有望进一步提升至 852 亿元,同比增长 22%。尽管中国先进封装产业整体体量已位居全球前列,但据锐观产 业研究院数据,2024 年先进封装渗透率仅为 40%,显著低于全球平均水平的 55%,渗透 率有望持续提升,为行业打开长期成长空间。

国产 OSAT 龙头持续追赶,四家大陆厂商进入全球 top10 OSAT。当前中国先进封装市 场玩家由 OSAT 企业主导,长电科技份额领跑,随后为通富微电、华天科技、智路封测 等。根据芯思想 2024 年全球 OSAT 企业排名,四家大陆厂商进入全球前十,合计市占率 为 27.8%,且较 23 年有所提升,形成与中国台湾地区四家封测龙头(市占率 34.9%)相 抗衡的格局。中国大陆 OSAT 龙头已迈入全球第一梯队,但在高端先进封装产能、关键 工艺平台和国际客户结构方面,仍与台系头部及美资巨头存在一定差距。未来随着产能 持续扩张和技术平台迭代,本土企业有望进一步提升全球话语权,加速追赶国际先进水 平。

(二)产业供需结构错配与政策支持叠加,国产先进封装产业迎来发展机遇

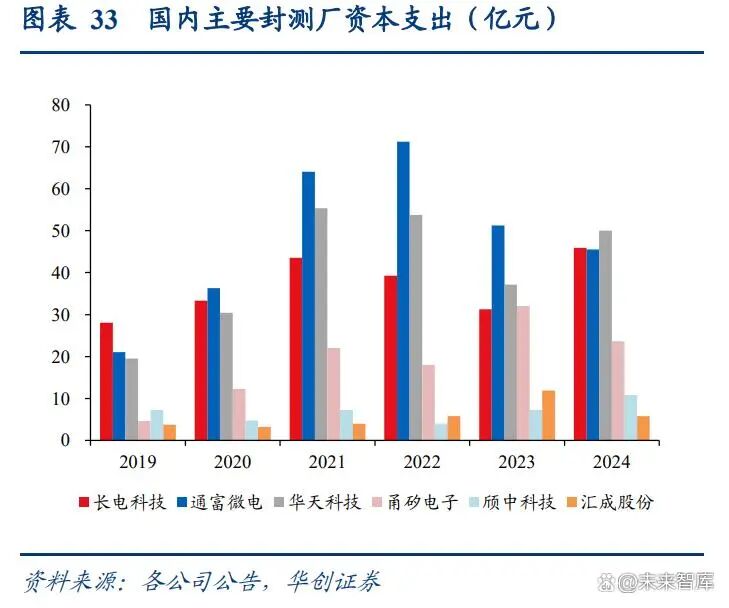

需求牵引平台升级,国产先进封装从“跟跑”向“并跑”迈进。早期本地先进封装平台基础 相对薄弱,在 2.5D/3D、Chiplet 互联等关键工艺环节技术积累有限,曾一度依赖台积电、 三星等海外封装方案,例如,据半导体产业纵横报道,华为曾是台积电首个 CoWoS客户;三星披露百度的首代昆仑芯片也采用了其 I-Cube 技术进行封装。近年来中国芯片设 计产业快速发展,AI 加速器、通用 GPU、车规 SoC 等高性能芯片方向取得显著进展,先 进芯片设计需求反向推动本土封测厂商加快平台建设与工艺迭代,封装平台能力正成为 国产高端芯片实现产业化的关键支点。 国内领先企业加速追赶业内龙头厂商,近年来资本支出显著提升。集成电路产业具有技 术开发、更新换代快的特点,要封装企业紧随产业链上下游的技术步伐,需投入大量资 金用于开发先进的封装技术。国内封装龙头在生产规模和技术水平上不断追赶业内龙头 厂商,资本支出有所提升,资本密集度较高。其中 2024 年长电科技、通富微电、华天科 技的资本支出分别为 45.91、45.54、50.01 亿元,占营业收入比例分别为 13%、19%、35%。

海外产能紧张+供应链自主化诉求升温,为本土平台创造验证窗口。当前部分先进封装产 能趋紧,据 IT 之家援引经济日报报道,尤以台积电称 CoWoS 产能目前严重供不应求, 除了自身扩产还需联手日月光、Amkor 等合作伙伴协同增产,力求 2025 年总月产能突破 7.5 万片。需求井喷,部分次梯队客户及长尾订单或将出现结构性外溢。叠加地缘摩擦加 剧,本土终端客户在先进半导体产业链对国产替代路径敏感度提高,海外客户奉行“China for China”战略,为中国封装企业创造了技术磨炼与信任建立的时间窗口,也成为国产平 台切入高端异构封装价值链的关键机会。 国家层面持续强化对先进封装平台能力建设的资金与政策支持。近年来,国家层面持续 加大对先进封装产业链的资源支持与政策投入。长电科技、通富微电、华天科技等头部 厂商均获得国家集成电路产业投资基金一、二期扶持,推动其在 Fan-out、2.5D/3D 封装、 Chiplet 异构集成等平台能力上实现技术突破。2024 年 5 月,国家集成电路产业投资基金 三期注册成立,注册资本达 3440 亿元,超过前两期大基金总和,预计会赋能半导体制造、 先进封装、设备、材料等关键领域,加快国内先进芯片制造领域突破卡脖子的进程。

四、先进封装市场群雄逐鹿,IDM、Fab、OSAT 玩家并存

全球先进封装市场集中度高,委外代工模式仍占据全球主要份额。全球封测企业主要分 为代工厂 Fab、垂直整合制造商 IDM、独立封测代工厂 OSAT 三类。终端产品多样化推 动封测设计趋于复杂,IDM 封测的研发费用升高,而头部 OSAT 厂商由于技术积累及成 本优势,目前仍占全球先进封装主要份额。2022 年 IDM 占全球先进封装 22.6%市场份 额,Fab 占 12.3%,OSAT 达 65.1%市场份额。仅看 OSAT 市场份额,根据芯思想研究院, 2024 年前三大 OSAT 厂商依然把控半壁江山,市占率合计超过 50%。

先进封装马太效应明显,技术领先的龙头厂商有望享受市场红利。随着封装技术朝小型 化和集成化方向发展,先进封装难度不断提升,行业壁垒逐渐提高。高端先进封装技术 如 2.5D/3D 集中于部分 OSAT 龙头及台积电、英特尔等提供封装服务的晶圆厂。头部 OSAT 厂商不断追赶先进技术,日月光、安靠已掌握 3D 堆叠,国内长电科技、通富微电、 华天科技均有开发各自平台覆盖 2.5D/3D。未来,Chiplet 所带动的 2.5D/3D 技术含量快 速提升,高利润赋能企业提高研发及资本投入强度,进而形成强者恒强的局面,技术领 先的龙头厂商有望享受最大红利。

(一)全球龙头各有所长,台积电加码自研工艺平台领跑全球

1、台积电:CoWoS+InFO+SoIC 构建 3D Fabric 平台

台积电在先进封装领域起步早、投入大,是全球先进封装技术和产能布局的行业领军者。 2008 年台积电设立集成互连与封装开发部门(IIPD),2011 年即率先推出 CoWoS 平台, 2020 年又正式发布 3DFabric 计算平台,覆盖 SoIC(前端 3D 堆叠)、CoWoS 与 InFO(后 端先进封装)等多元技术路线,为同构和异构集成客户提供全方位解决方案。公司凭借 持续创新和强大产能,实现与 NVIDIA、AMD、苹果等全球头部芯片设计企业的深度绑 定,成为 AI、高端消费电子和先进逻辑芯片的首选代工与封装平台。 CoWoS 平台持续迭代,成为 AI 及高性能计算主流封装方案。CoWoS(Chip-on-Wafer-onSubstrate)是台积电最具代表性的 2.5D/3D 先进封装平台,其架构可分为两部分:CoW (Chip-on-Wafer)阶段,将芯片堆叠于硅中介层上;WoS(Wafer-on-Substrate)阶段,则 将完成堆叠的中介层整体封装到有机基板上。该技术利用硅通孔(TSV)与微凸块实现互 连,能够将 GPU、AI 加速器等先进逻辑芯片与 HBM 模块紧密集成,有效缩短数据传输 路径并提升吞吐量,为 AI 训练、高性能计算(HPC)等带宽和算力需求极高的场景提供 理想解决方案。

自 2012 年率先量产 CoWoS 以来,围绕封装尺寸、布线能力及集成密度持续优化,台积 电 CoWoS 形成了 CoWoS-S/R/L 3 个版本: (1) CoWoS-S:采用单片硅中介层+硅通孔 TSV实现芯片与基板之间的高速电信号传输, 但大尺寸单片硅中介层在制造中存在良率瓶颈,限制了进一步放大封装面积的能力。 (2) CoWoS-R:以有机中介层+细间距重布线层(RDL)取代 CoWoS-S 的硅中介层,可 在 HBM 与逻辑芯片之间以及芯片与基板之间提供高速互连。RDL 能够缓冲基板与 中介层热膨胀系数不匹配引起的应力,提升封装可靠性与良率。 (3) CoWoS-L:采用局部硅互连(LSI)+RDL 中介层构成重组中介层,在保留硅通孔(TSV) 高速互连优势的同时,减少大面积硅中介层带来的良率问题。此外,CoWoS-L 支持 在逻辑芯片下方集成额外元件的能力,例如独立的 IPD(集成无源器件),使其具有 更好 SI/PI 性能。

CoWoS 经历 6 代迭代,演进方向围绕扩大中介层尺寸与提升可集成 HBM 容量。2011 年,第一代 CoWoS 采用最大尺寸约 775mm²(28mm×28mm)的硅中介层,最多可搭载一 颗 HBM。第三代 CoWoS 实现了 GPU 逻辑芯片与 HBM 的首次组合封装,并在后续版本 中不断增加可集成的 HBM 数量,同时持续升级 HBM 规格。发展至 2023 年的第六代, 硅中介层尺寸已扩展至 3400mm²(58mm×58mm),可在单封装内搭载多达 12 颗 HBM。 然而,中介层面积的扩大也带来了良率挑战:晶圆边缘的中介层更易出现缺陷,从而减 少了单片 12 英寸晶圆可切割出的合格中介层数量。

InFO 平台聚焦 Fan-Out 市场,推动移动与高性能终端结构创新。InFO(Integrated Fanout)是台积电于 2016 年量产的一种晶圆级系统集成技术,属于 FOWLP(Fan-Out Wafer Level Packaging)先进封装范畴,通过高密度 RDL 与 InFO 通孔(TIV)实现无需有机封 装基板的高密度互连。

InFO-PoP(集成式扇出型堆叠封装)是业界首款 3D 晶圆级扇出封装方案。通过高 密度 RDL 与 TIV,将移动应用处理器与 DRAM 直接堆叠集成,省去有机基板与 C4 凸块,使封装更薄、信号路径更短,并具备优异的电气与热性能,尤其适合对空间 和能效要求极高的智能手机和平板终端。

InFO-oS(基板上集成扇出型封装)面向高密度互连需求,采用先进的 2/2µm 线宽/ 间距 RDL,可在封装中集成多个高性能逻辑芯片,并支持小至 40µm 的混合 I/O 焊 盘间距。这一高密度互连能力特别适用于 5G 网络设备与计算密集型任务,为下一代网络基础设施和高算力应用提供关键支撑。

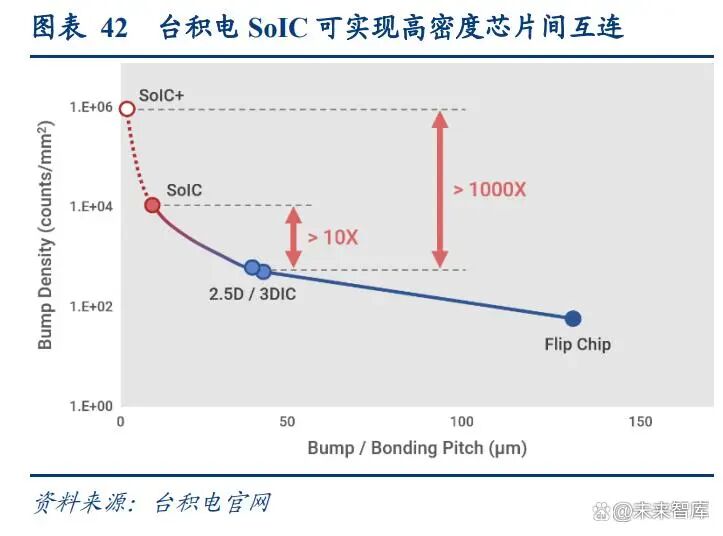

SoIC 平台实现高密度 3D Chiplet 堆叠,布局未来系统级集成。SoIC(System on Integrated Chips)是台积电 3DFabric 的前端 3D 堆叠技术,也是业内首个高密度 3D Chiplet 堆叠方 案。SoIC 通过混合键合在芯片间构建直接互连界面,支持多层、多尺寸及多功能芯片的 垂直集成,大幅提升互连密度并减小封装尺寸。平台包括 CoW(Chip-on-Wafer)与 WoW (Wafer-on-Wafer)两种形态,适配逻辑、存储及异构芯粒的灵活组合,满足未来高算力 与高集成系统的演进需求。

2、英特尔:布局 EMIB 与 Foveros 两大平台技术

英特尔以 EMIB 与 Foveros 双平台构造先进封装体系,夯实异构集成技术护城河。公司 将先进封装视为其IDM 2.0战略的关键,围绕EMIB与Foveros两大平台,形成覆盖2.5D、 3D 及混合架构的多元化工艺体系,旨在实现多芯粒异构集成、功能模块化和系统级灵活 扩展。公司战略目标是实现 2030 年封装 1 万亿个晶体管。

EMIB 技术以嵌入式硅桥实现高性价比 2.5D 互连,提升良率与集成效率。EMIB 通 过在基板中嵌入小尺寸硅桥,实现多芯片高速互连,相较于传统大尺寸硅中介层方 案,具备优势:(1)成本优化:硅桥面积小,晶圆利用率高,降低材料与制造成本; (2)良率提升:省略晶圆级封装步骤,减少凸点、模具等复杂工艺的良率损失风险; (3)生产效率:制造步骤更少、复杂度更低,缩短生产周期;(4)尺寸优化:硅 桥嵌入基板,提高面积利用率,使单一封装可集成更多芯片以承载更大工作负载。

Foveros 实现主动中介层 3D 堆叠,支持高带宽、低功耗垂直集成。Foveros 是英特 尔的3D封装平台,通过在主动式中介层上结合TSV实现不同类型芯片的垂直整合, 支持逻辑、存储及 I/O 等多功能模块的三维异构集成。Foveros 2.5D 和 3D 采用基于 焊料的互连方式,而非基底连接,适用于高速 I/O 与小型芯片分离设计;Foveros Direct 3D 则通过铜-铜直接键合,实现更高互连带宽与更低功耗,提升系统性能与能效比。

EMIB 3.5D 融合 2.5D 与 3D 优势,支撑多模块异构系统集成。EMIB 3.5D 技术结合 EMIB与Foveros平台,在单一封装内实现多个3D堆叠模块的高速互连与协同工作, 适配高复杂度、多制程节点、多功能模块的系统设计。在实际应用中,英特尔数据 中心 GPU Max 系列 SoC 即采用 EMIB 3.5D 技术,集成超过千亿个晶体管,包含 47 个有源模块,跨越 5 个不同制程节点,充分体现了英特尔在大规模异构集成上的技 术领先性。

3、三星电子:I-Cube 与 X-Cube 双平台布局 2.5D/3D 异构集成

推进 I-Cube 与 X-Cube 平台布局,覆盖 2.5D/3D 先进封装技术。三星电子于 2022 年 12 月,在半导体业务部门内成立了先进封装(AVP)业务团队,以加强先进封装技术。三星 的先进封装技术主要分为两大类:属于 2.5D 封装的 I-Cube 和属于 3DIC 的 X-Cube:

I-Cube 系列属于 2.5D 异构集成。通过水平并列布局实现逻辑芯片与 HBM 高带宽 存储的高效互连,兼顾散热与扩展性能。I-Cube S 采用硅中介层;I-Cube E 则采用硅 嵌入式中介层结构,结合硅桥精细布线和 TSV 结构 RDL 中介层优势,在保障信号 完整性的同时,提升良率与大尺寸适配能力。在 I-Cube S 的基础上,H-Cube 平台将 ABF(Ajinomoto Build-up Film)和 HDI(高密度互连)基底工艺结合,实现更大尺 寸封装与多功能芯片集成。

X-Cube 技术属于 3D 异构集成。基于 TSV 硅通孔技术实现芯片间的垂直电气互连, 提升带宽密度和信号传输效率。X-Cube 平台分为 bump 凸点互连与 Hybrid Bonding 混合键合两种工艺路径:前者以传统微凸点实现芯片堆叠;后者以铜-铜混合键合为 核心,芯片布局更具灵活性,且三星正在持续推进 4μm 超精细的铜混合键合技术 的开发。

(二)本土 OSAT 封测厂具备优势,不断拓宽先进封装平台布局

1、长电科技:国产先进封装技术平台布局完善

公司先进封装技术覆盖全面,在晶圆级封装、2.5D/3D 领域具备独特优势。公司拥有行业 领先的半导体先进封装技术,包括利用 RDL、TSV、Bumping、硅互联等技术的高集成度 的晶圆级 WLP、2.5D/3D、系统级(SiP)封装技术和高性能的 Flip Chip 和引线互联封装。 同时,公司正积极开发 3D 封装技术,以满足市场对下一代高密度器件日益增长的需求, 实现更高的集成度、模块的功能和更小的尺寸,增强公司技术壁垒。

倒装封装:技术布局全面,涵盖 FcBGA、FcCSP、FcLGA、FcPoP、FCOL 产品组合。 公司提供丰富的倒装芯片产品组合,从搭载无源元器件的大型单芯片封装,到模块 和复杂的先进 3D 封装,包含多种不同的低成本创新选项。

系统级封装:公司布局多年,在 SiP 封装的优势体现在双面塑形技术、EMI 电磁屏 蔽技术、激光辅助键合(LAB)3 种先进技术。公司 SiP 技术广泛应用于 SSD、CPU、 GPU、APU、PMIC、射频等产品。

晶圆级封装:公司在晶圆级封装技术方面处于行业领先地位,提供的解决方案包括 扇入型晶圆级封装(FIWLP)、扇出型晶圆级封装(FOWLP)、集成无源器件(IPD)、 硅通孔(TSV)、包封芯片封装(ECP)、射频识别(RFID)。

2.5D/3D:公司积极推动传统封装技术的突破,率先在晶圆级封装、倒装芯片互连、 硅通孔(TSV)等领域中采用多种创新集成技术,以开发差异化的解决方案,帮助客 户在其服务的市场中取得成功。

2、通富微电:多元化先进封装布局与国际大客户协同发展

持续强化高端先进封装能力,深度绑定国际核心客户与高景气赛道。公司依托在传统 QFN、LQFP 等框架类封装及 FCBGA、FCCSP 等基板类封装领域的深厚积累,近年来加 快布局 Fan-out、WLCSP、倒装焊(FC)、2.5D/3D 堆叠、Chiplet 等高端先进封装技术, 形成涵盖主流与前沿的多元产品结构。作为 AMD 全球最大封测供应商,公司在槟城等 基地重点建设 Bumping、EFB 等核心产线,“合资+合作”深化与国际头部客户的协同开 发与本土化服务能力,驱动先进封装业务实现规模扩张。凭借与富士通、卡西欧、AMD等全球一线客户的技术许可合作及协同开发优势,公司正加速在高性能计算、存储、AI 等先进封装核心应用市场实现份额突破。

3、华天科技:eSinC 技术对标 CoWoS,发力国产 2.5D/3D 先进封装

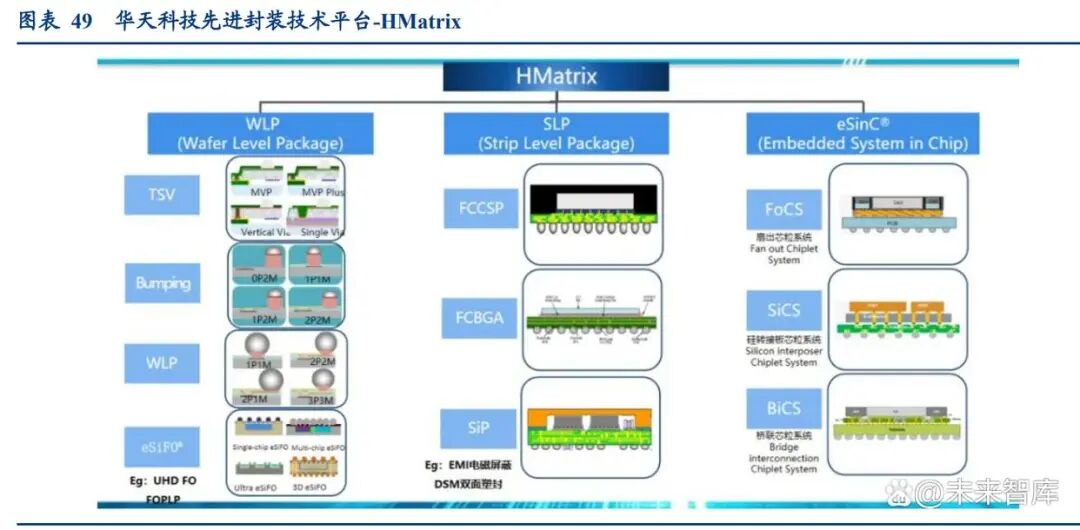

重视技术创新和产品结构升级,发力先进封装平台化布局。公司率先掌握了 SiP、FlipChip、TSV、Bumping、Fan-Out、WLP、3D 等多项先进封装工艺,现有封装技术水平及 科技研发实力已处于国内同行业领先地位。公司构建先进封装技术平台 HMatrix,覆盖包 括 WLP、SLP、eSinC 等技术方向,并在 2.5D/3D 领域布局 RDL 中介层、硅中介层、3D Stack 及铜-铜混合键合等多种关键技术。2024 年,公司完成 2.5D 产线建设和设备调试, FOPLP 技术通过重点客户认证,Chiplet 产品开发也在有序推进。 其中,华天科技 eSinC 技术平台对标 CoWoS 相关技术:

SiCS:采用硅转接板实现多芯粒互连的 2.5D 先进封装技术,这种结构通常具有高密 度的 I/O 互连及优越的电性能,适合高性能计算和大规模集成电路的需求。

FoCS:采用机械灵活性更强的 RDL 作为中介层来实现芯片之间的互连,主要用于 降低成本并适应不同类型的器件连接需求,具有更大的设计灵活性,能够支持更多 的芯片连接。

BiCS:采用 LSI 芯片实现高密度的芯片间互连,这些芯片可以具有多种连接架构, 并且可以重复用于多个产品,基于模具的中介层较宽的 RDL 层间距,并采用穿透中 介层的通孔来实现信号和电力的低损耗高速传输,能够集成额外的元件。

加码产能整合,20 亿组建先进封测公司。2025 年 8 月,公司宣布整合华天江苏、华天昆 山及华天先进一号基金资源,20 亿元注册资本共同组建南京华天先进封装有限公司,强 势进军 2.5D/3D 先进封装赛道。此举有望加速前沿产能释放与技术商业化进程,助力国 内 2.5D/3D 先进封装测试技术的进步和产业升级。

4、盛合晶微:国产 WLCSP 封装龙头,深耕三维先进封装技术

深耕三维集成与中段工艺,夯实大陆先进封装创新高地。公司前身为中芯长电,是全球 首家采用集成电路前段芯片制造体系和标准,采用独立专业代工模式服务全球客户的中 段硅片制造企业。公司创新研发三维多芯片集成封装结构方案和平台技术 SmartPoser, 并已建立起覆盖芯粒多芯片集成的全流程制造体系和量产能力。根据盛合晶微官网援引 CIC 灼识咨询《全球先进封装行业研究报告》,2023年公司 12 英寸 WLCSP 市场份额位 居中国大陆首位,并是大陆唯一规模量产硅基 2.5D 芯粒加工的企业,在先进封装中段制 造环节具备优势。

重视研发投入,推进多项先进封装平台进步。2024 年 5 月,盛合晶微推出 3 倍光罩尺寸 的 TSV 硅通孔载板技术,标志其芯片互联技术正式进入亚微米时代,可进一步提升芯粒 间互联密度,为未来高性能异构集成奠定基础,在先进封装制高点持续保持先发优势。 目前公司已启动科创板上市进程,并于 2025 年 6 月进入辅导验收阶段。未来有望在资本 支持下进一步强化其在高端先进封装领域的综合技术实力与行业影响力。

5、甬矽电子:定位中高端封装赛道,推进 Fan-out 与 2.5D/3D 布局

持续强化中高端先进封装业务布局,一站式能力与新工艺布局驱动成长。公司产品均为 QFN、LGA、BGA、FlipChip、Bumping、WLCSP 等中高端先进封装形式,并在系统级封 装(SiP)、高密度细间距凸点倒装产品(FC 类产品)、大尺寸/细间距扁平无引脚封装 产品(QFN/DFN)、Bumping/WLP 等先进封装领域具有较为突出的工艺优势和技术先进 性。公司重点打造的“Bumping+CP+FC+FT”的一站式交付能力不断提升,有效客户群持 续扩大,量产规模稳步爬升,贡献了新的营收增长点。24 年,公司通过实施 Bumping 项 目已掌握 RDL 及凸点加工能力,并积极布局 Fan-out 及 2.5D/3D 封装工艺,相关产品线 均已实现通线,目前正在与部分客户进行产品验证。

6、晶方科技:晶圆级 TSV 持续突破,布局 CIS 晶圆级封装细分赛道

晶圆级 TSV 封装技术的领先者,差异化布局以影像传感芯片为代表的传感器市场。公司 避开通用封装红海市场,重点布局汽车电子与 AI 端侧等高成长细分领域。顺应汽车智能 化趋势,公司自主开发了超薄晶圆级芯片尺寸封装技术、硅通孔封装技术、扇出型封装 技术、系统级封装技术及应用于汽车电子产品的封装技术等,并持续优化 TSV-STACK 等 高端工艺,拓展 A-CSP 等创新方案,增加量产规模,提升生产效率,进一步巩固在车规 CIS 封装领域的技术优势与业务规模。同时,公司积极响应产业升级节奏,实现 AI 眼镜、机器人等新兴应用方向的产品商业化量产,进一步巩固差异化竞争优势和未来成长空间。

五、相关标的

(一)长电科技:国内封测龙头,全面布局先进封装加速成长

公司是全球领先的半导体封测厂商,布局先进封装实现业务稳步扩张。公司自其前身 1972年成立以来,专注于半导体封装测试行业,目前是中国大陆第一、全球第三大封测 厂商。公司内生外延持续进行国际化布局,目前在全球拥有八大集成电路成品生产基地, 分别位于上海、江阴、滁州、宿迁、新加坡和韩国,实现主流封测技术全覆盖。公司着力 先进封装业务,目前已覆盖 WLP、2.5D/3D、SiP、高性能 Flip Chip 等市场主流封装工艺, 并加速从消费类向市场需求快速增长的汽车电子、5G 通信、高性能计算、存储等高附加 值市场的战略布局。未来公司持续拓展先进封装业务,有望为营收提供增长动力,规模 效应下公司利润弹性有望加速释放。 行业周期回暖驱动封测需求复苏,高带宽推动先进封装市场加速增长。目前全球下游终端智能手机销售情况已同比回正,上游 IC 设计公司库存调整接近尾声,参考历史周期规 律,我们认为半导体行业景气度已开始逐步回暖。集成电路封测属于重资产行业,具有 资本密集与人员密集特点,产能利用率提升为盈利关键,景气度上行趋势下公司利润弹 性大。封装行业技术持续进步,受益于 HPC、AI 快速发展催生高带宽需求,先进封装市 场规模加速增长。竞争格局方面,全球先进封装市场集中度较高,OSAT 模式仍为主导, 其中日月光、安靠、长电科技等中国大陆及台湾厂商占据全球主要份额。先进封装市场 马太效应明显,行业壁垒随技术发展而逐渐提高,长电科技加速布局 2.5D/3D 高端先进 封装技术,未来成长空间广阔。 公司国产龙头封测厂商,先进封装卡位优势明显。公司为全球第三/中国大陆第一的封装 大厂,传统封装与先进封装技术覆盖全面,具备明显卡位优势,且紧跟产业技术路线研 发最先进技术以强化竞争壁垒。公司与通信、消费等领域全球头部大客户开展合作,目 前已覆盖西部数据、高通、海力士、TI 等厂商,客户资源优质。2024 年 9 月 30 日,公 司宣布收购晟碟半导体 80%股权已完成交割,本次收购有助于加强与西部数据的战略联 系,进一步强化公司在存储领域的 OSAT 龙头厂商地位。

(二)通富微电:汽车电子业务高速增长,与 AMD 持续深化合作

行业复苏叠加产品结构优化带动收入增长,资本开支加码夯实成长动能。受益于下游需 求回暖、先进技术突破与策略优化成效,2025Q1 公司实现营业收入 60.92 亿元,同比增 长 15.34%。归母净利润/扣非归母净利润分别为 1.01/1.04 亿元,同比增长 2.94%/10.19%。 归母净利润增速相对滞后,主要系折旧相关的税会差异及子公司盈利增长带动所得税费 用大幅上升,单季所得税支出达 7920 万元,同比增长 679.96%。忽略所得税扰动看,公司营业利润为 2.06 亿元,同比增长 63.03%,核心盈利能力仍有改善。公司披露规划 2025 年资本开支 60 亿元,其中 35 亿元将用于通富超威苏州与槟城基地扩产升级,未来伴随 先进制程产能逐步释放及产品结构优化,公司长期成长空间有望进一步打开。 AI 驱动先进封装需求爆发,公司掌握优质客户资源,内生外延布局先进技术。AI 算力芯 片及存储器需求激增带动先进封装市场高增长,公司作为 AMD 最大封测供应商(占其 订单 80%+),持续深化合作, 2024 年 AMD 的年度营业额达到创纪录的 258 亿美元, 为 公司的营收规模提供了有力保障。技术布局方面,公司内生布局 Chiplet、2D+等前沿技 术,2024 年玻璃基板(TGV)封装已通过可靠性测试,并通过收购京隆科技 26%股权补 强测试能力,技术竞争力进一步巩固。

汽车电子、存储业务高增长,中长期成长动能充足。业务布局方面,公司加速向高端领 域转型,1)汽车电子方面,公司全面拓展车载功率器件、MCU 与智能座舱等产品,2024 年营收同比+200%;2)存储封测方面,公司深化与原厂战略协同,2024 年营收增速超 40%;3)消费电子方面,公司抓住手机产品国产国造机遇,成为重要客户的策略合作伙 伴,实现了中高端手机 SOC46%的增长。产能扩张方面,2024 年通富超威苏州/槟城完成 Bumping、EFB 等产线建设,南通三期、通富通科等重大项目建设稳步推进,新增施工面 积 24.45 万平米,为后续产能扩张奠定坚实基础。

(三)晶方科技:汽车 CIS 驱动高增长,持续推进全球化布局

晶圆级影像传感器封装引领者,技术优势下业绩保持稳健。公司是全球将晶圆级芯片尺 寸封装(WLCSP)专注应用在以影像传感器为代表的传感器领域的先行者与引领者。晶 圆级芯片尺寸封装技术的核心工艺优势包括晶圆级、硅通孔(TSV)、三维 RDL 等工艺 能力,具备晶圆级空腔和晶圆级堆叠封装结构,并能提供微型化、低功耗、高集成、高性 能的解决方案。2025 年一季度,公司实现营业收入 2.91 亿元,同比增长 20.74%,实现归 母净利润 0.65 亿元,同比增长 32.73%,业绩延续稳健趋势。 手机/安防需求回暖,汽车 CIS 构筑第二增长曲线,积极布局机器人新兴市场。消费领域, 据 IDC 统计 2024 年全球智能手机出货量同比增长 6.1%至 12.36 亿部,据群智咨询预计 安防 CIS 出货量同比增长 2%至 4.9 亿颗,公司凭借晶圆级封装技术在中低像素市场的优 势,承接下游回暖需求,业务企稳回升;汽车电子成为最大亮点,公司建成全球首条 12 英寸车规级 TSV 封装量产线,与豪威、思特威等头部客户深度合作。受益于汽车智能化 推动的车用 CIS 需求大幅增长,公司在车规级封装领域的技术优势逐步兑现。据 Sigmaintell 预测,2020-2029 年汽车 CIS 出货量 CAGR 达 13.46%,公司技术卡位高景气 赛道,未来增长空间广阔。此外,公司也在积极布局 AI 眼镜、机器人等新兴市场。

持续深化全球化布局,第三代半导体打开成长空间。公司持续推进国际化战略:1)光学 领域,荷兰 Anteryon 与苏州晶方光电协同,晶圆级光学器件(WLO)工艺不断提升,公 司积极推进在汽车智能投射等领域的产品应用;2)功率半导体领域,整合以色列 VisIC 的氮化镓技术,布局车用高功率模块,把握新能源汽车电驱系统升级机遇;3)在马来西 亚投建生产基地,贴近海外客户需求,增强供应链韧性。2025 年 Q1 公司研发投入 0.33 亿元,同比+11.33%,占营业收入比例为 11.42%,技术护城河持续加固。

(本文仅供参考,不代表我们的任何投资建议。如需使用相关信息,请参阅报告原文。)

>>>查看更多:股市要闻